AI Chip Report

: Analysis on the Market, Trends, and TechnologiesThe AI chip market is accelerating rapidly: the data available reports a 2021 market size of $13.64 billion and projects growth to $429.35 billion by 2032 at a 36.8% CAGR, driven by data-center demand for large models, a fast expansion of edge inference use cases, and intense venture funding activity (the funding pool analyzed totals $9.61 billion). This combination of surging LLM workloads, migration of inference to edge and enterprise on-prem deployments, and material advances in memory-centric and chiplet architectures will force vendors to optimize power, latency, and software stacks as primary competitive levers.

This report was last updated 202 days ago. Spot an error or missing detail? Help us fix it by getting in touch!

Topic Dominance Index of AI Chip

To identify the Dominance Index of AI Chip in the Trend and Technology ecosystem, we look at 3 different time series: the timeline of published articles, founded companies, and global search.

Key Activities and Applications

- Data-center training and inference for large language and vision models — hyperscalers and cloud providers remain the largest buyers, and demand for transformer-optimized accelerators drives specialized ASIC and wafer-scale design activity marketresearch - 2025.

So what: vendors that reduce cost per token and improve throughput per watt capture the highest value in cloud contracts. - Edge inference for real-time systems (autonomous vehicles, smart cameras, IoT gateways) — designers prioritize NPUs and low-power ASICs to meet latency and energy budgets.

So what: optimizing for inference performance per millijoule opens massive addressable markets in automotive, industrial automation, and wearables. - On-premise enterprise inference and model hosting — organizations seek hardware alternatives to cloud spend for privacy and cost reasons, favoring inference-optimized silicon and turnkey stacks.

So what: suppliers that combine hardware with a deployable software ecosystem can win sticky enterprise contracts. - Processing-in-memory (PIM) and analog in-memory inference — activity concentrates on eliminating data-movement bottlenecks to cut latency and power for transformer inference at scale.

So what: PIM and analog approaches can deliver order-level energy advantages for edge and large-model inference. - AI-assisted EDA and automated chip design — firms apply agentic and ML tools to shorten tapeout cycles and optimize power-performance-area tradeoffs.

So what: faster design cycles compress time-to-market and lower non-recurring engineering risk for challengers.

Emergent Trends and Core Insights

- Memory-centric computing becomes mainstream — in-chip memory and compute-near-memory patents and product roadmaps indicate a structural shift to reduce data movement as the principal performance limiter and.

So what: architectures that colocate weights and computation will redefine cost and power baselines for LLM inference. - Chiplet and heterogeneous die integration scale rapidly — modular chiplets and advanced die-to-die interconnects enable mixed-process, cost-effective designs for high aggregate compute and.

So what: ecosystem players supplying interposers, IP, and validated chiplet stacks will capture margin in packaging and integration services. - Analog, spintronic, and neuromorphic approaches target extreme efficiency at the edge — multiple startups and funding rounds show investor appetite for alternative device physics to lower power by orders of magnitude and.

So what: these technologies offer differentiated value where battery life and always-on processing matter. - Software-hardware co-design and compiler ecosystems gain strategic value — hardware without an optimized stack sees adoption friction; SDKs and model compilers become sale drivers and Axelera.

So what: incumbents that own a full stack (silicon plus SDK) erect durable barriers to entry. - Geopolitics and on-shore funding reshape capacity allocation — government subsidies and national programs alter where critical fabs, packaging, and IP development concentrate researchandmarkets - 2025.

So what: supply-chain resilience and localized partnerships become procurement priorities.

Technologies and Methodologies

- Processing-in-Memory and Compute-in-Memory (PIM / CIM) — addresses the memory wall by embedding compute with weight storage, delivering higher effective throughput per watt and vendors such as PIMIC.ai focus on in-memory edge solutions.

- Analog in-memory compute and charge-domain circuits — trade precision for dramatic power savings, suitable for edge inferencing and sensor fusion and companies like GEMESYS pursue analog training/inference innovations.

- Neuromorphic and spiking neural architectures — event-driven processing and mixed-signal designs for ultra-low power sensing and closed-loop control.

- Chiplet ecosystems and advanced 2.5D/3D packaging — die modularity paired with high-bandwidth interconnects lets teams mix mature nodes for analog IO, HBM stacks for memory, and advanced compute dies Chipletz and.

- Silicon photonics and photonic interconnects — optical links reduce power and increase rack-level bandwidth for data-center scale LLM deployments.

- AI-driven EDA and generative design agents — ML agents accelerate layout, verification, and PPA tuning, shortening tapeout cycles and reducing iteration costs and companies like PrimisAI and llmda apply these methods PrimisAI llmda.

AI Chip Funding

A total of 173 AI Chip companies have received funding.

Overall, AI Chip companies have raised $19.0B.

Companies within the AI Chip domain have secured capital from 739 funding rounds.

The chart shows the funding trendline of AI Chip companies over the last 5 years

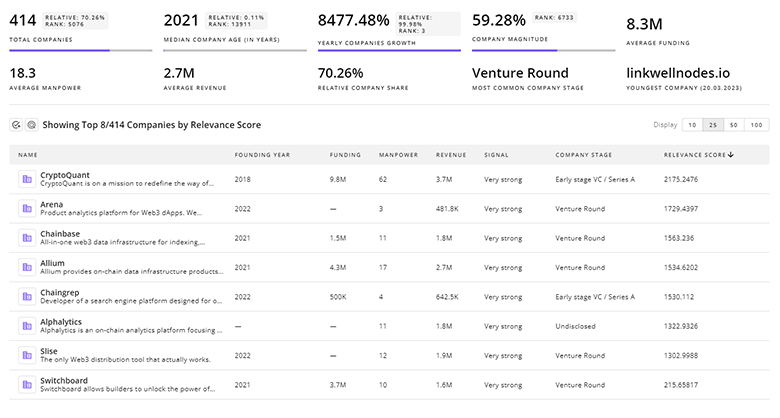

AI Chip Companies

- SEMRON — SEMRON claims a high "intelligence density" NPU architecture that uses 3D scaling and CapRAM-style analog memory to run much larger models at lower investment and energy cost; the company targets always-on smartphone and wearable AI use cases and positions its tech as a path to always-available on-device models.

- GEMESYS — GEMESYS develops analog brain-inspired chips that aim to deliver extreme energy efficiency for on-device training and inference; the stack targets decentralized edge scenarios where training cost, dataset size, and energy are limiting factors.

- Fractile — Fractile designs compute-memory fused chips targeting LLM inference bottlenecks by eliminating repeated weight movement; the architecture promises large speedups for transformer inference and targets cloud and on-prem inference farms where cost per token matters.

- PIMIC.ai — PIMIC focuses on processing-in-memory architectures for ultra-low-power edge AI, advertising 50x compute and 20x power reductions for inference tasks such as speech recognition; the product roadmap emphasizes sensor-level integration and sub-microamp target currents.

- Corintis — Corintis supplies microscale, embedded cooling channels and chip-level thermal management for high-density AI dies; its approach addresses the thermal limit that increasingly constrains multi-die and high-power accelerators in racks and edge boxes.

Identify and analyze 719 innovators and key players in AI Chip more easily with this feature.

719 AI Chip Companies

Discover AI Chip Companies, their Funding, Manpower, Revenues, Stages, and much more

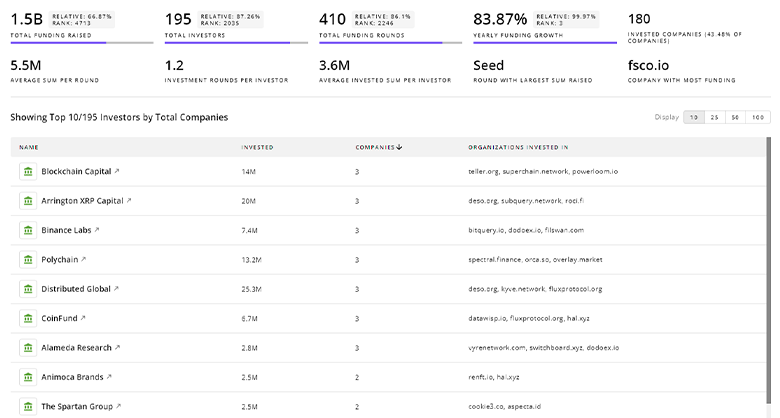

AI Chip Investors

TrendFeedr’s investors tool offers a detailed view of investment activities that align with specific trends and technologies. This tool features comprehensive data on 1.4K AI Chip investors, funding rounds, and investment trends, providing an overview of market dynamics.

1.4K AI Chip Investors

Discover AI Chip Investors, Funding Rounds, Invested Amounts, and Funding Growth

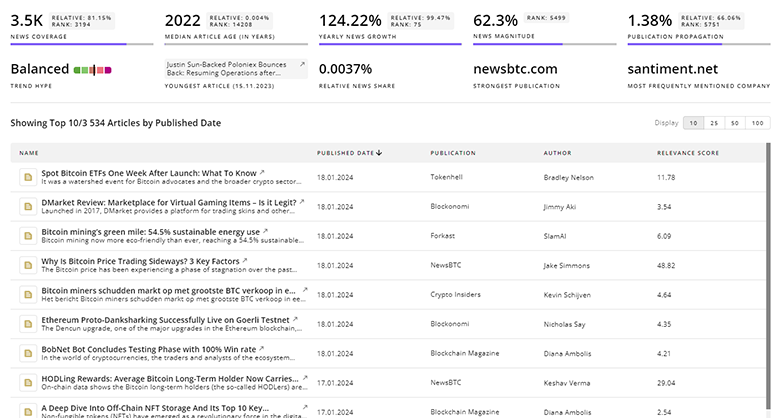

AI Chip News

Stay informed and ahead of the curve with TrendFeedr’s News feature, which provides access to 9.7K AI Chip articles. The tool is tailored for professionals seeking to understand the historical trajectory and current momentum of changing market trends.

9.7K AI Chip News Articles

Discover Latest AI Chip Articles, News Magnitude, Publication Propagation, Yearly Growth, and Strongest Publications

Executive Summary

The AI chip market presents a clear, actionable set of strategic priorities for investors, OEMs, and compute operators. First, prioritize architectures that materially reduce data movement—PIM, in-memory compute, and analog approaches—and combine those with credible SDKs to make adoption simple. Second, plan product lines using chiplet modularity and advanced packaging to balance cost and performance across cloud and edge segments. Third, invest in thermal and interconnect solutions as part of the compute stack because power density—not raw transistor count—will limit usable performance in production. Finally, use funding and partnership signals to identify niche insurgents with viable IP for extreme-efficiency edge inference and partner with them to differentiate product portfolios while managing supply-chain and geopolitical exposure.

Interested in enhancing our coverage of trends and tech? We value insights from experts like you - reach out!